无题

学习verilog

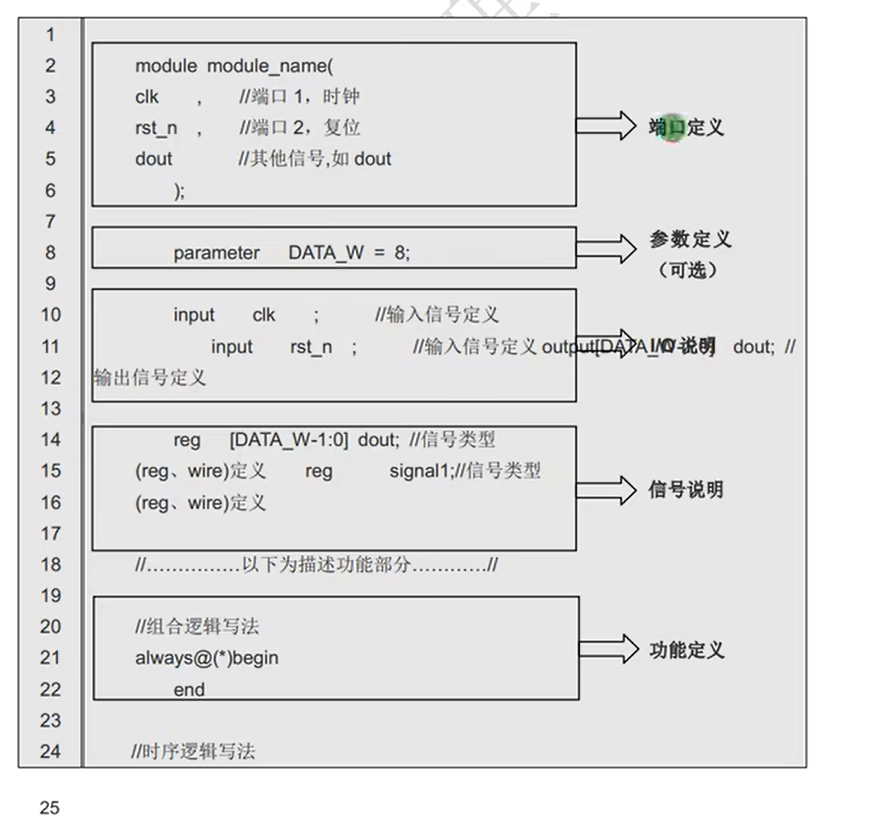

万事万物皆模块

两种模式方式:

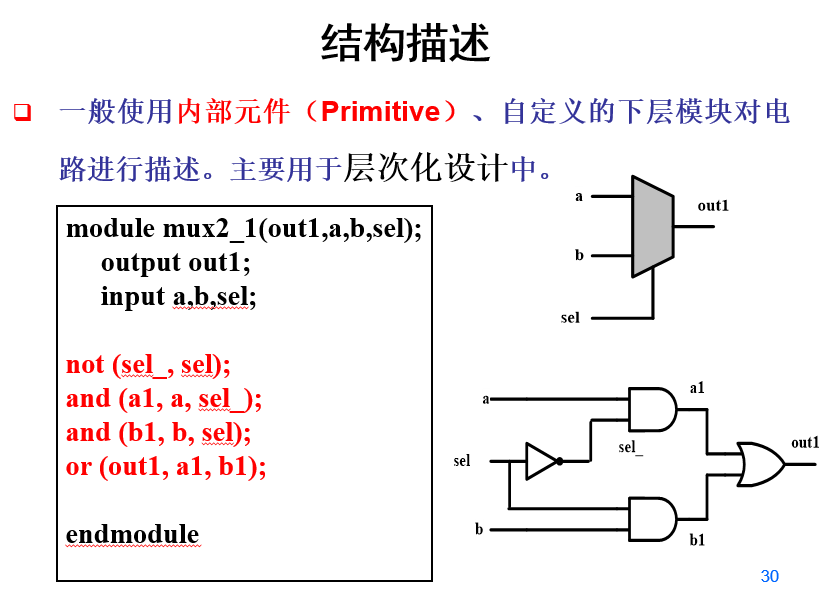

- 结构描述

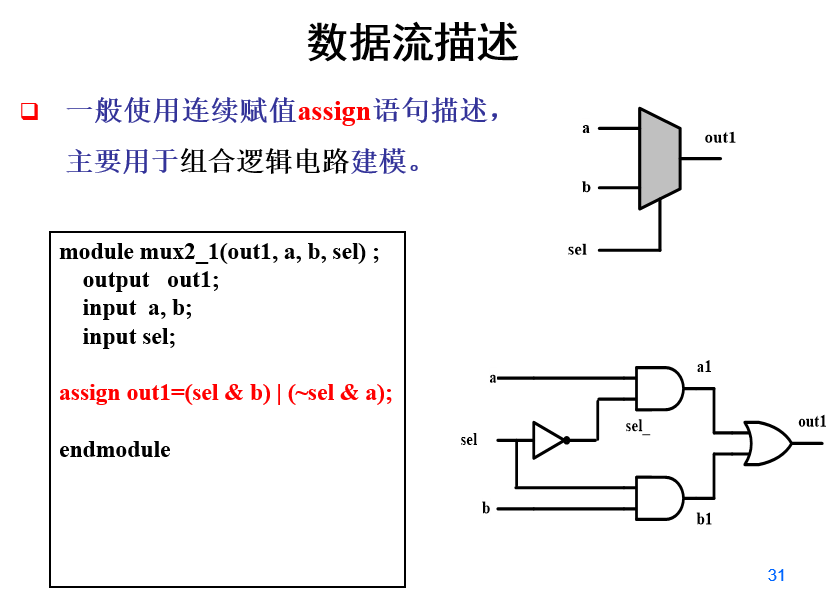

- 数据流描述

always 表示一直都会运行

reg 寄存器

wire 线网

这两个是信号类型

常量的格式:W’Bval(位宽’ 进制(二进制-b,八进制-o,十进制-d,十六进制h)数值)

例如:

- 1’b0—单bit信号二进制信号(等价于十进制0)

- 4’b0011—4bit二进制信号0011(等价于十进制3)

- 8’hff—8bit十六进制ff(等价于十进制255)

- 8’d255—6bit十进制255

块语句

1)起始块:仅在起始的时候执行一次,仅在testbench中出现

1 | initial begin |

2)always 块:当敏感列表发生变化时会执行

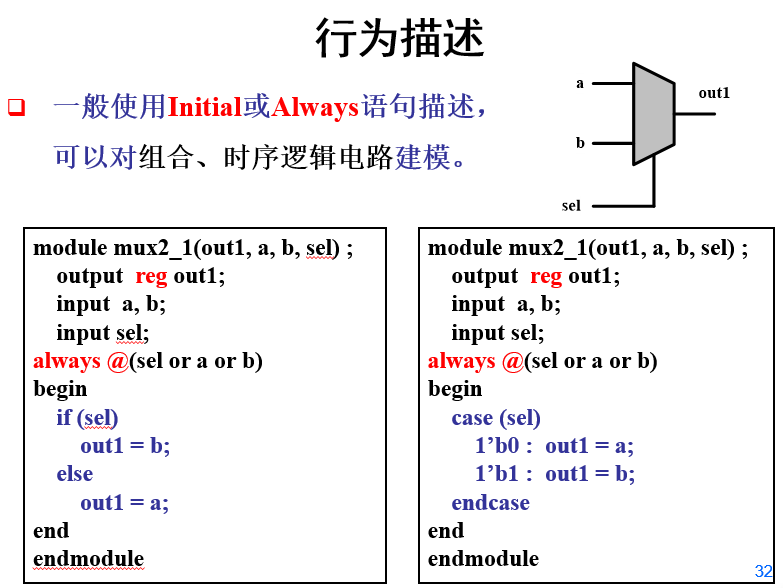

行为描述方式

1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行 , 或者说此语句重复执行。 只有寄存器类型数据能够在这两种语句中被赋值。寄存器类型数据在被赋新值前保持原 有值不变。所有的初始化语句和 a l w a y s语句在0时刻并发执行。

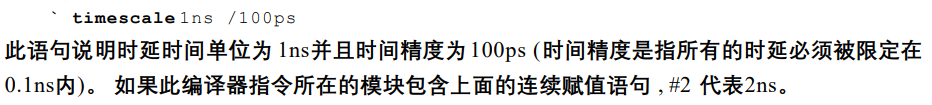

时延可以细分为两种类型:

1) 语句间时延: 这是时延语句执行的时延。

2) 语句内时延: 这是右边表达式数值计算与左边表达式赋值间的时延。

3) 下面是语句间时延的示例:

S u m = (A ^ B) ^ C i n;

4 T 1 = A & C i n;

在第二条语句中的时延规定赋值延迟 4个时间单位执行。就是说,在第一条语句执行后等待 4 个时间单位,然后执行第二条语句。

4) 下面是语句内时延的示例。

S u m = #3 (A^ B) ^ C i n;

这个赋值中的时延意味着首先计算右边表达式的值 , 等待3个时间单位,然后赋值给S u m。

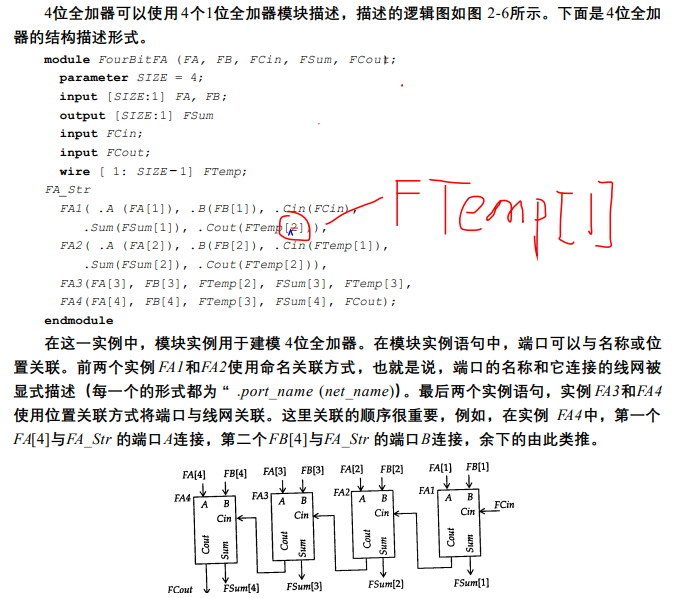

结构化描述形式

1) 内置门原语(在门级);

2) 开关级原语(在晶体管级);

3) 用户定义的原语(在门级);

4) 模块实例 (创建层次结构)。 通过使用线网来相互连接。下面的结构描述形式使用内置门原语描述的全加器电路实例。

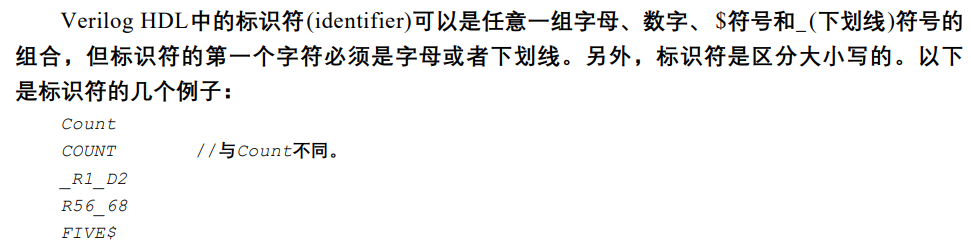

标识符

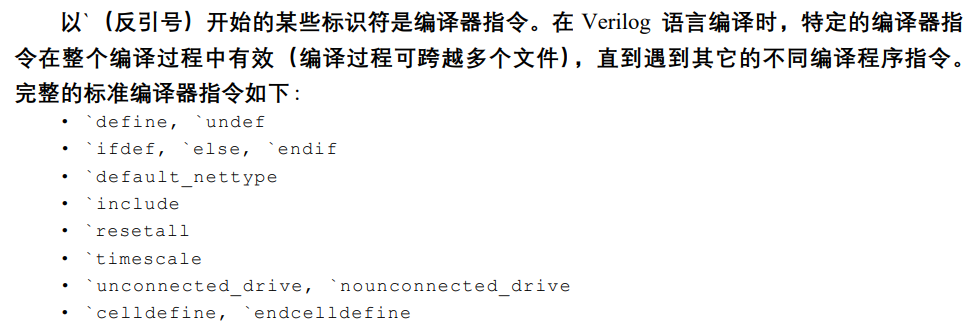

编译指令

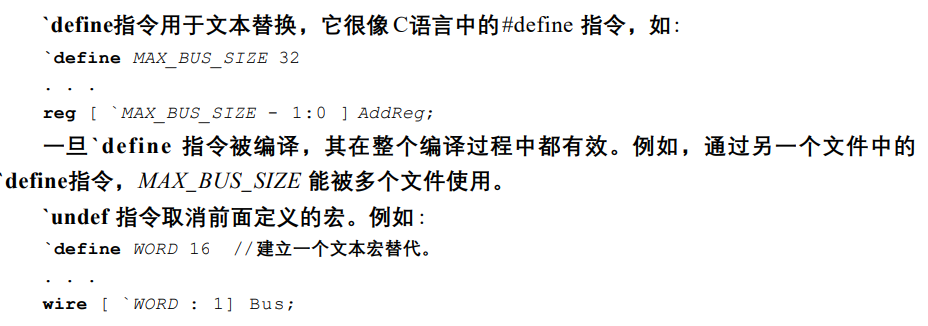

define 和undef

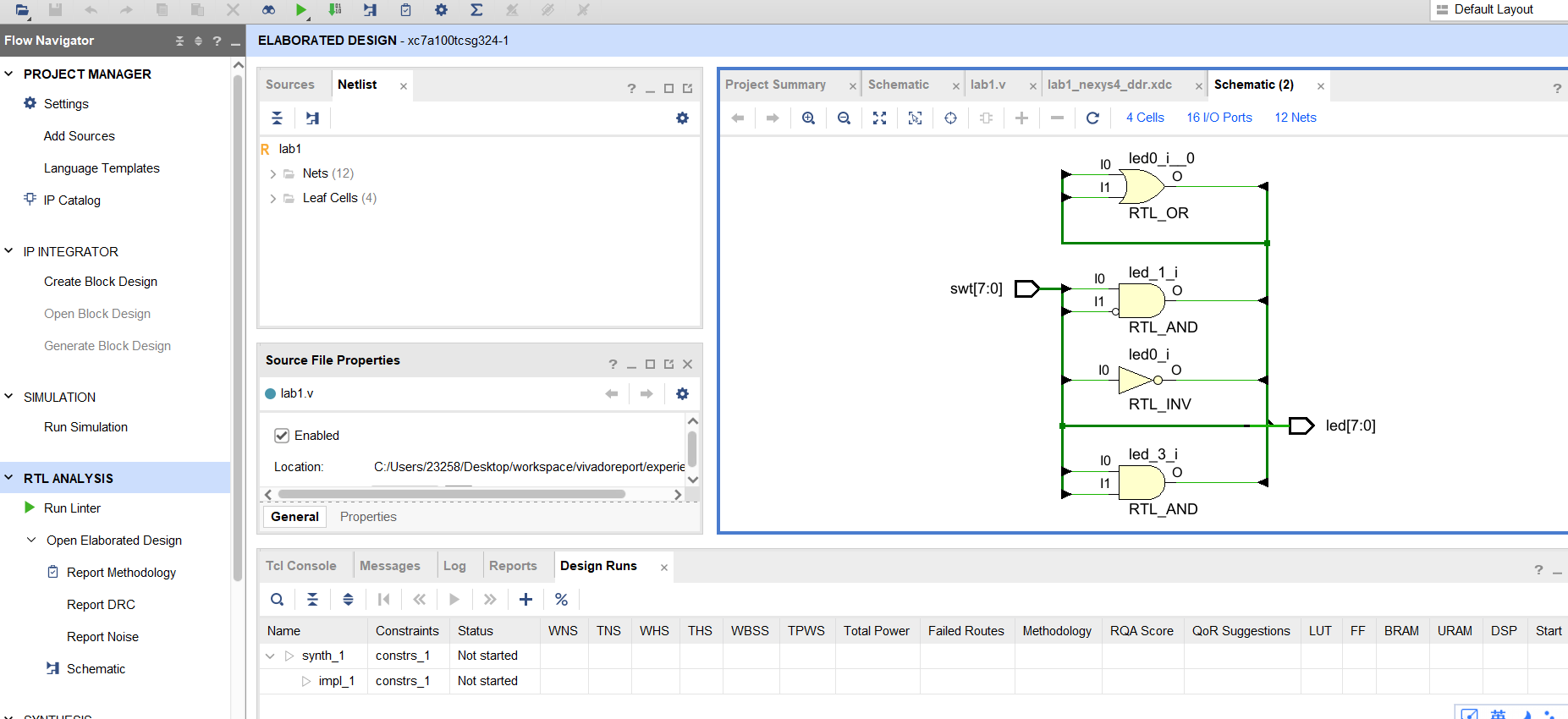

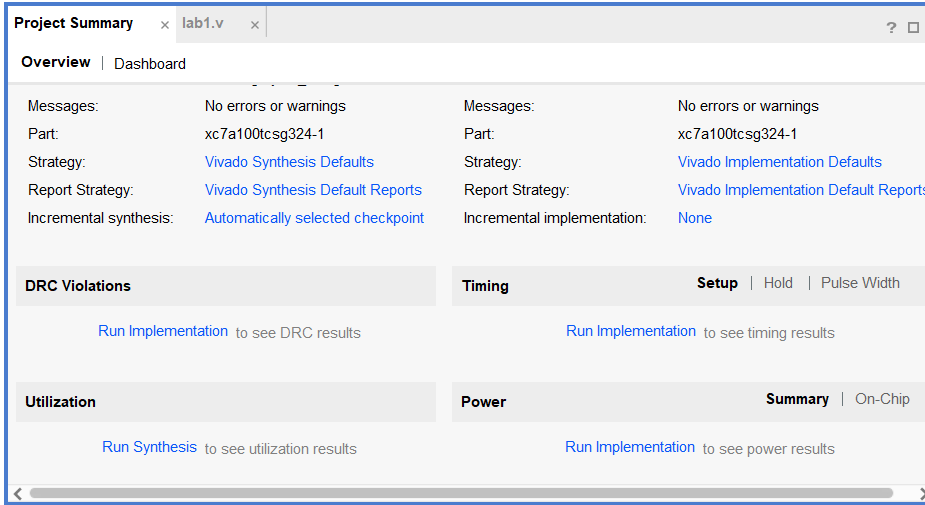

vivado

这是可以看到封装

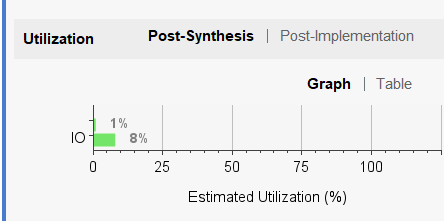

可以看利用率

查看原理

wire类型的信号不能在过程块中进行直接赋值操作

定义成

1 | output reg [7:0] SEG; |

才可以在always赋值

1 | 如果你移除 reg 关键字,即将声明修改为 output [7:0] SEG;,那么 SEG 将成为一个组合逻辑输出。这意味着你不能在 always 块中对其进行赋值操作,而是应该使用连续赋值语句(如 assign)来定义其逻辑实现。 |

.in 是一种用于连接模块实例的语法。它表示将一个信号或变量连接到模块的输入端口。

在 Verilog 中,当实例化一个模块时,需要将模块的输入端口与其他信号或变量进行连接。这可以通过在模块实例化语句中使用 .in 语法来完成。

例如,在代码中的一行中使用了 .in 语法:

verilog

复制

1 | decoder_3to8(.in(SW[15:13]), .out(AN[7:0])); |

这行代码实例化了一个名为 decoder_3to8 的模块,并将 SW[15:13] 连接到模块的输入端口,通过 .in 来指定连接。这意味着 SW[15:13] 将作为 decoder_3to8 模块的输入信号。

.out 语法也被用于连接模块的输出端口,如代码中的 .out(AN[7:0]),它将模块的输出端口 AN[7:0] 与该信号进行连接。